## Testing Digital Systems I

# Lecture 10: Boolean Testing Using Fault Models (FAN)

Instructor: M. Tahoori

Copyright 2010, M. Tahoori

TDS I: Lecture 10

1

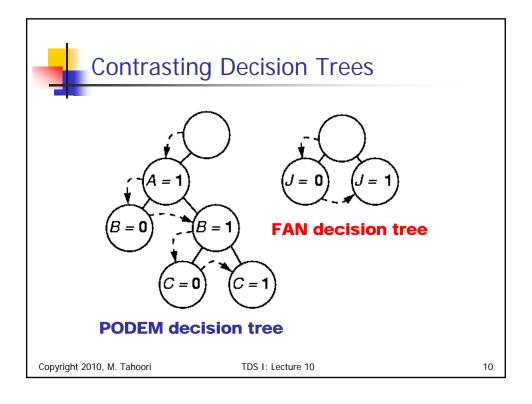

#### **FAN**

- Internal and Input values assigned (FAN)

- New features

- Stop Backtraces at Head Lines

- Input Lines or Internal Lines that Cannot Cause Conflict

- To reduce the number decisions

- Immediate Implication

- Both Forward and Backward

- Unique Sensitization

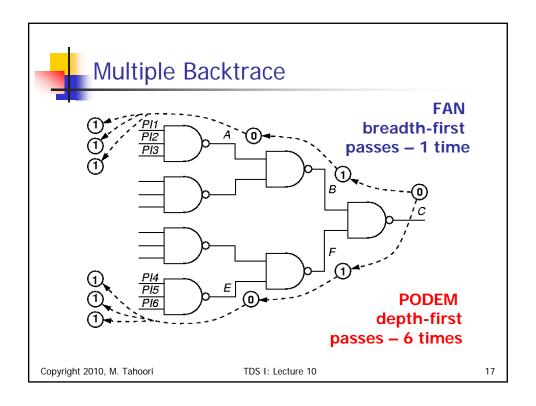

- Multiple rather than Single Backtrace

- Multiple Objectives to reduce later conflicts

Copyright 2010, M. Tahoori

TDS I: Lecture 10

2

Lecture 10

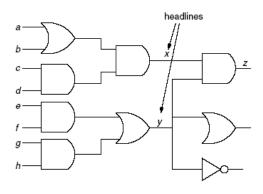

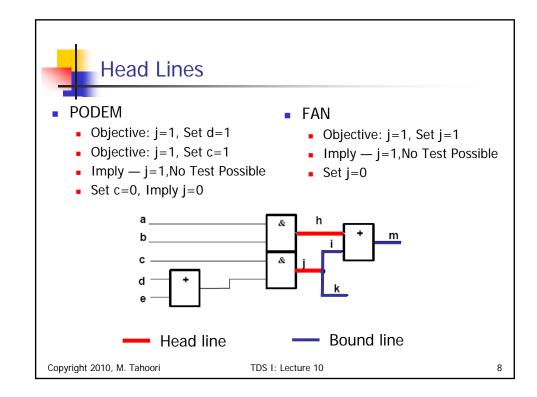

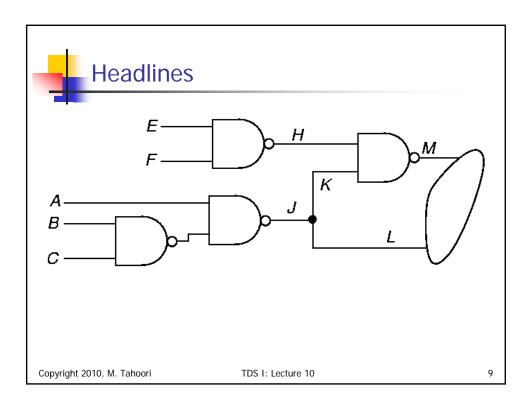

### Headlines

- Output signals of fanout-free cones

- Any value on headlines can always be justified by the PIs

We only need to backtrace to the headlines to reduce the number of decisions

Copyright 2010, M. Tahoori

TDS I: Lecture 10

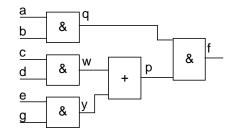

### Fanout-Free Network

- Justify logic value 1 on f

- Justify 1 on p and q

- a = b = c = d = 1

- Justify logic value 0 on f

- a = 0

- A fanout-free logic network with no redundancy

- the logic value at the output of the logic network can always be justified without any backtracking

Copyright 2010, M. Tahoori

TDS I: Lecture 10

4

### **Head-Lines**

- Bound Line

- Any signal line which directly or indirectly fed by a fanout branch

- Free Line

- Line that is Not Bound

- Head Line:

- Free Line, and

- Fanout Stem or Input of a Gate with Bound Output,

Copyright 2010, M. Tahoori

TDS I: Lecture 10

5

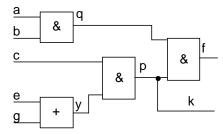

### **Head-Lines**

- f, f2 and k are the bound lines

- a, b, q, c, e, g, y and p are free lines

- p and q are head lines

- p is a fanout stem and q is the only free signal line which is an input of a gate whose output is a bound line (f)

Copyright 2010, M. Tahoori

TDS I: Lecture 10

6

#### Testing Digital Systems I

#### How to mark?

- Start at the primary inputs of the logic network which are marked as free lines and move forward towards the output

- Whenever encounter a fanout

- Mark each fanout branch as a bound line

- If the fanout stem is a free line

- Mark it as a head line

- When encounter a logic gate,

- The output of that gate is a bound line if and only if any of the inputs of that gate is a bound line;

- Otherwise, the output of the logic gate is a free line

- If the logic gate output is a bound line

- Any input of that gate which is a free line is marked as a head line

Copyright 2010, M. Tahoori

TDS I: Lecture 10

7

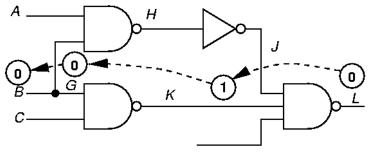

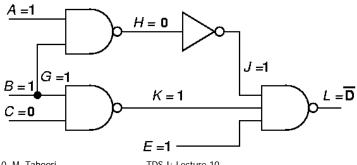

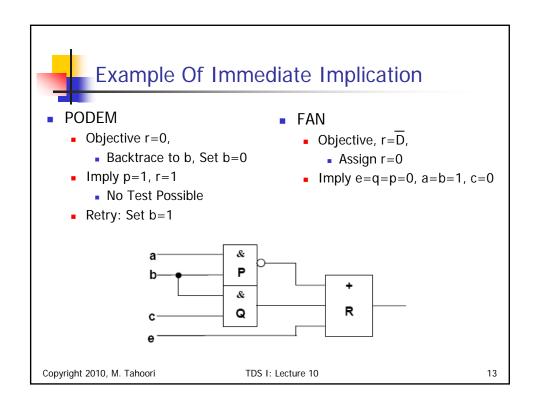

## **Immediate Implication**

- PODEM Fails to Determine Unique Signals

- Backtracing operation

- fails to set all 3 inputs of gate L to 1

- Causes unnecessary search

Copyright 2010, M. Tahoori

TDS I: Lecture 10

11

# **Immediate Implication**

- FAN -- Early Determination of Unique Signals

- Determine all unique signals implied by current decisions immediately

- Avoids unnecessary search

Copyright 2010, M. Tahoori

TDS I: Lecture 10

Lecture 10 6

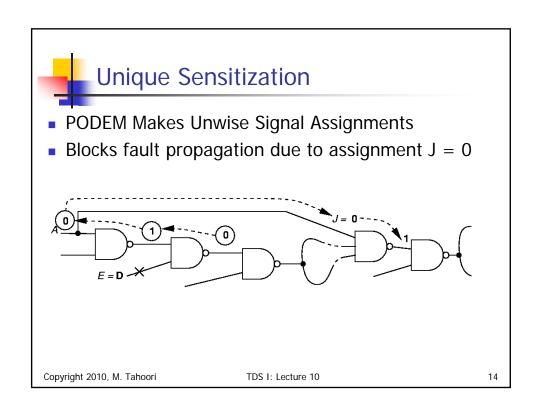

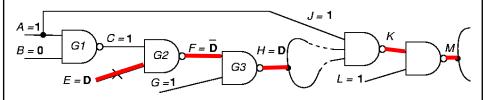

## **Unique Sensitization**

- Unique Sensitization of FAN with No Search

- FAN immediately sets necessary signals to propagate fault

Path over which fault is uniquely sensitized

Copyright 2010, M. Tahoori

TDS I: Lecture 10

15

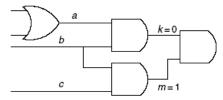

# **Multiple Objectives**

- Objectives: {k=0, m=1}

- Backtrace from k=0 may favor b=0, but simulate(b=0) would violate the second objective m=1!

- Makes backtrace more intelligent to avoid future conflicts

Copyright 2010, M. Tahoori

TDS I: Lecture 10

16

### Testing Digital Systems I