# Testing Digital Systems I

#### Lecture 8:

Boolean Testing Using Fault Models (D Algorithm)

Instructor: M. Tahoori

Copyright 2010, M. Tahoori

TDS I: Lecture 8

1

# Specific-Fault Oriented Test Generation

- Three Approaches

- Internal Line Values Assigned ( D Algorithm) (Roth-1966)

- D-cubes

- Bridging faults

- Logic gate function change faults

- Input Values Assigned (PODEM) (Goel 1981)

- X-Path-Check

- Path propagation constraints to limit ATPG search space

- Backtracing

- Input and Internal Values Assigned (FAN) (Fujiwara)

- Efficiently constrained backtarce

Copyright 2010, M. Tahoori

TDS I: Lecture 8

2

# D-Algorithm -- Roth IBM (1966)

- Fundamental concepts invented:

- First complete ATPG algorithm

- D-Cube

- D-Calculus

- Implications forward and backward

- Implication stack

- Backtrack

- Test Search Space

Copyright 2010, M. Tahoori

TDS I: Lecture 8

5

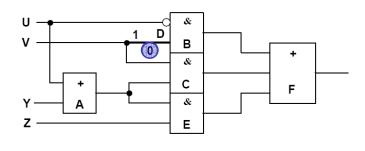

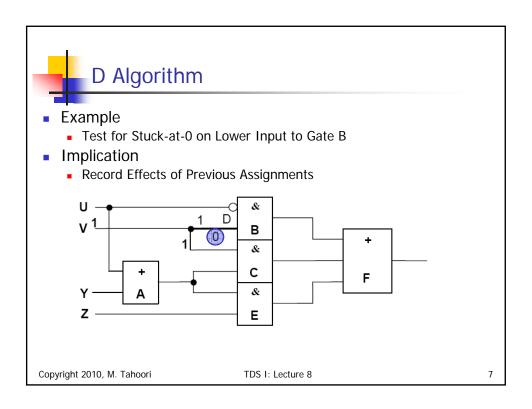

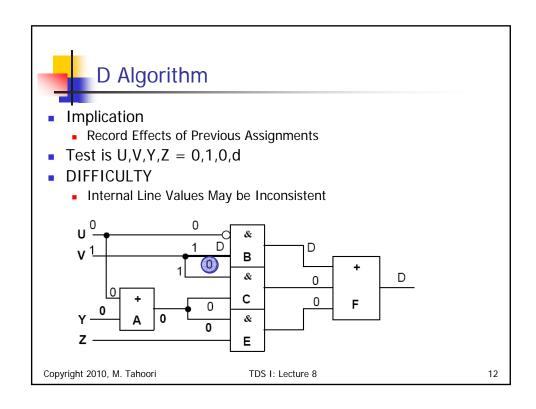

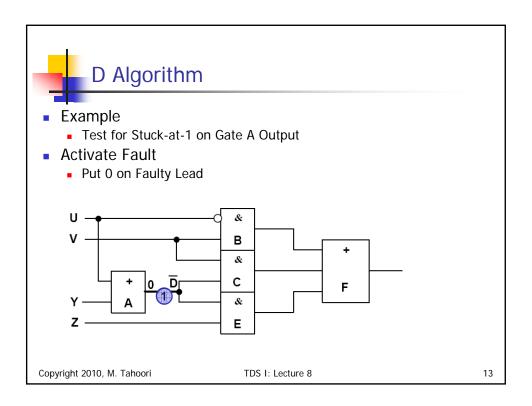

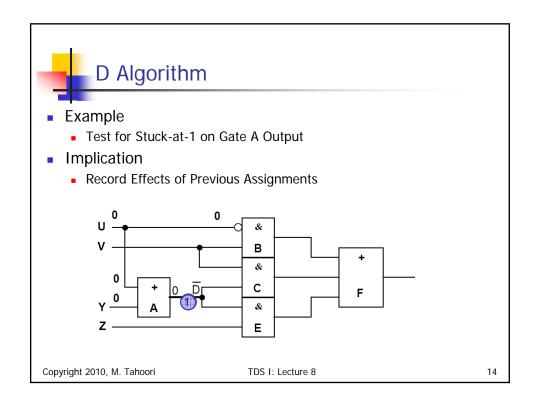

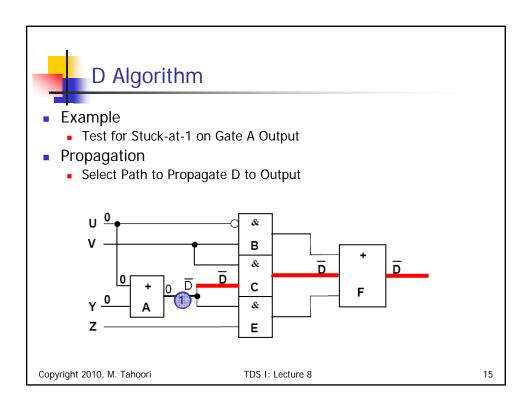

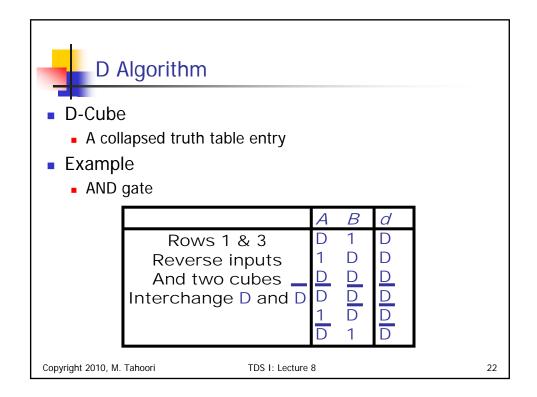

## D Algorithm

- Assigning internal line values

- Example:

- Test for Stuck-at-0 on Lower Input to Gate B

- Activate Fault Put 1 on Faulty Lead

Copyright 2010, M. Tahoori

TDS I: Lecture 8

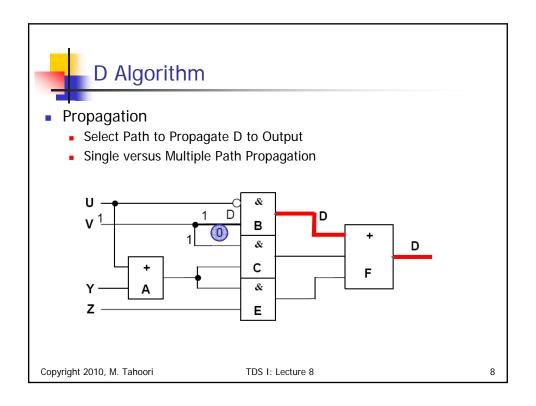

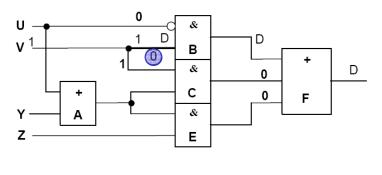

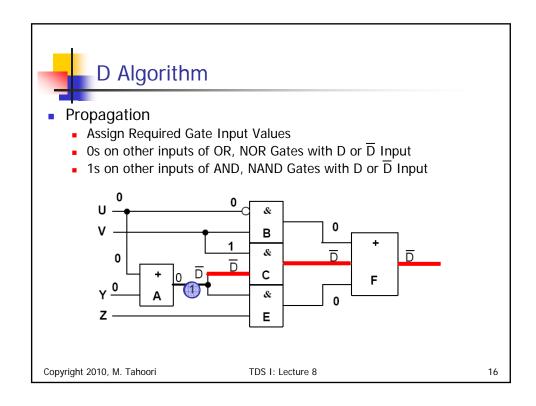

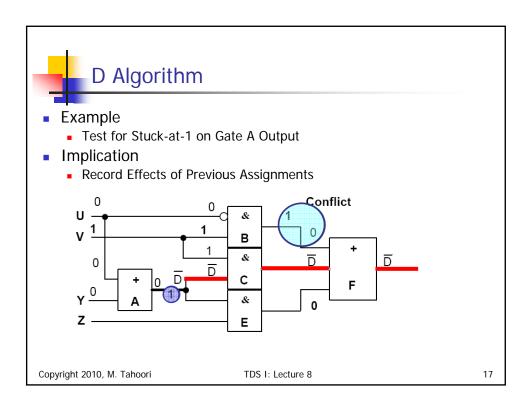

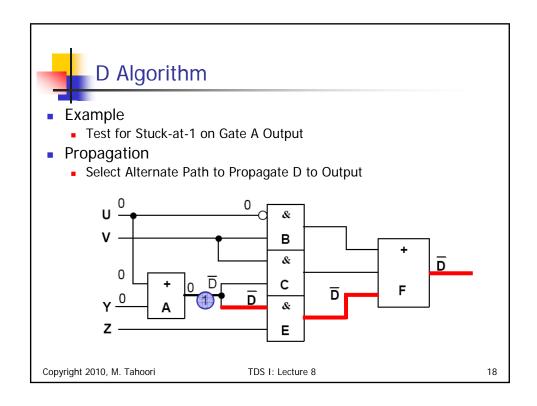

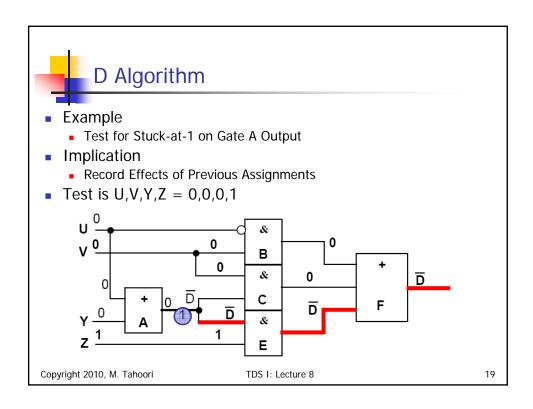

## D Algorithm

Propagation

Copyright 2010, M. Tahoori

- Assign Required Gate Input Values

- Os on other inputs of OR, NOR Gates with D or D Input

- 1s on other inputs of AND, NAND Gates with D or D Input

TDS I: Lecture 8

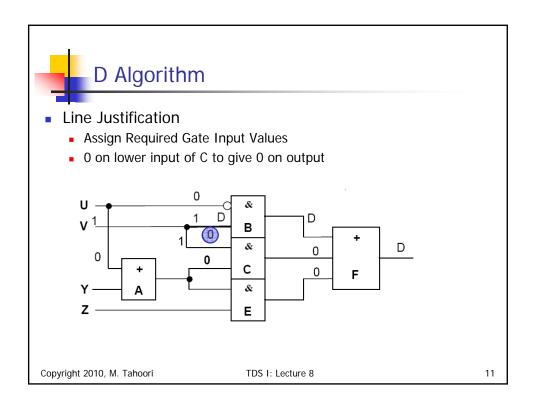

### Line Justification

- Find Input Assignment to Place Value v on Line g

- Path Tracing Approach

- Propagate Signals using Element Functions

- Must Choose Element Input Values and Paths

- Primitive cube of an element (gate) with output Z

- List of prime implicants of Z and Z'

|   | AND |   |   |  |  |  |  |  |

|---|-----|---|---|--|--|--|--|--|

| I | Α   | В | Z |  |  |  |  |  |

| I | 1   | 1 | 1 |  |  |  |  |  |

| I | 0   | _ | 0 |  |  |  |  |  |

|   | _   | 0 | 0 |  |  |  |  |  |

Implication (no choices)

Decision (choices)

Copyright 2010, M. Tahoori

TDS I: Lecture 8

10

#### Testing Digital Systems I

#### D Algorithm

- D Intersection

- Defines how different D-cubes can coexist for different gates in logic circuit

- If one cube assigns a specific signal value, the other cubes must assign either that same value or X

- $1 \cap 1 = 1 \cap X = X \cap 1 = 1$

- $0 \cap 0 = 0 \cap X = X \cap 0 = 0$

- X ∩ X = X

$\psi$ ,  $\phi$  represent incompatible assignments  $\mu$ ,  $\lambda$  represent incompatibility if both present

| $\cap$ | 0 | 1 | Χ | D | σĮ |

|--------|---|---|---|---|----|

| 0      | 0 | ф | 0 | Ψ | Ψ  |

| 1      | ф | 1 | 1 | Ψ | Ψ  |

| X      | Ó | 1 | X | Ď |    |

| D      | Ψ | Ψ | D | μ | λ  |

|        | Ψ | ψ | D | λ | μ  |

Copyright 2010, M. Tahoori

TDS I: Lecture 8

23

### **D** Algorithm

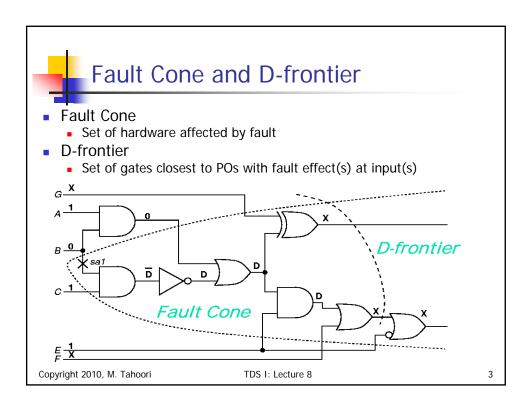

- Primitive D-cube of Failure (PDF)

- Models fault including

- SA1: represented by D

- SA0: represented by D

- Example: AND gate

- PDF for output SA0 is 1 1 D

- PDFs for output SA1 are 0 X D, X 0 D

- Propagation D-cube

- Models conditions under which fault effect propagates through gate

Copyright 2010, M. Tahoori

TDS I: Lecture 8

24

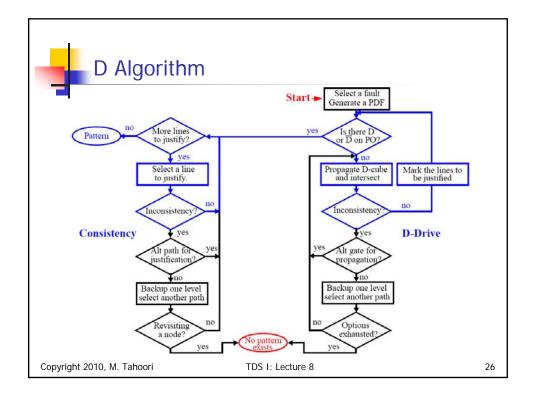

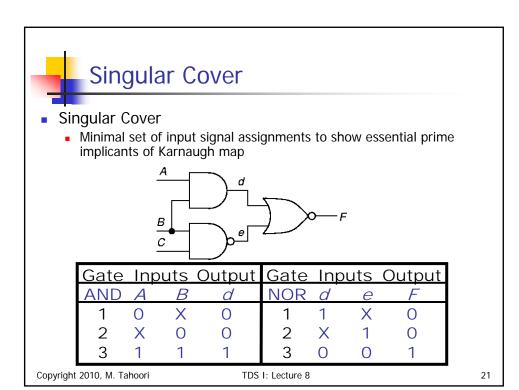

# **Implication Procedure**

- Model fault with appropriate PDF

- Select propagation D-cubes to propagate fault effect to a PO (D-drive procedure)

- Select singular cover cubes to justify internal circuit signals (Consistency procedure)

- D Algorithm's main problem

- Selects cubes and singular covers arbitrarily

Copyright 2010, M. Tahoori

TDS I: Lecture 8

25