## Testing Digital Systems I

## Lecture 12: Design for Testability

Instructor: M. Tahoori

Copyright 2019, M. Tahoori

TDS I: Lecture 12

#### History

- During early years, design and test were separate

- The final quality of the test was determined by keeping track of the number of defective parts shipped to the customer

- Defective parts per million (PPM) shipped was a final test score.

- This approach worked well for small-scale integrated circuit

- During 1980s, fault simulation was used

- Failed to improve the circuit's fault coverage beyond 80%

- Increased test cost and decreased test quality lead to DFT engineering

Copyright 2019, M. Tahoori

TDS I: Lecture 12

2

## History

- Various testability measures & ad hoc testability enhancement methods

- To improve the testability of a design

- To ease sequential ATPG (automatic test pattern generation)

- Still quite difficult to reach more than 90% fault coverage

- Structured DFT

- To conquer the difficulties in controlling and observing the internal states of sequential circuits

- Scan design is the most popular structured DFT approach

- Design for testability (DFT) has migration recently

- From gate level to register-transfer level (RTL)

Copyright 2019, M. Tahoori

TDS I: Lecture 12

2

## Design for Testability (DFT)

- Design techniques that are used to make testing of the resulting product economical

- Testability

- Easy to generate test patterns with "high" fault coverage within reasonable time

Copyright 2019, M. Tahoori

TDS I: Lecture 12

4

#### Challenge

- "Right" DFT technique to choose

- Observability and controllability play a major role in influencing the testability of a given IC

- *Observability* refers to the ease with which the state of internal signals can be determined at the circuit output leads.

- Controllability refers to the ease of producing a specific internal signal value by applying signals to the circuit input leads

- Improve testability

- Introduce test points, that is, additional circuit inputs and outputs to be used during testing

Copyright 2019, M. Tahoori

TDS I: Lecture 12

5

## Scan Architecture

Copyright 2019, M. Tahoori

TDS I: Lecture 12

7

#### Structured DFT

- Difficulty with the ad hoc testability techniques

- The requirement of adding extra control inputs or observation outputs

- Structured DFT techniques

- Permit access to internal nodes of a circuit without requiring a separate external connection for each node accessed

- At the cost of additional internal logic circuitry used primarily for testing

Copyright 2019, M. Tahoori

TDS I: Lecture 12

R

#### Scan Features

- Very few (from 1 to 4) additional external connections are used to access many internal nodes

- Typically all of the system bistable elements

- Serialization of the test data

- Otherwise, a large number of I/O pins will be required to control and observe logic values stored in each system bistable

- Test data must be transferred serially or scanned in and out of the circuit being tested.

- The change from normal system operation to test mode can be controlled by a level test-mode signal or by a separate test clock signal

Copyright 2019, M. Tahoori

TDS I: Lecture 12

9

#### Scan Features

- Most important advantage

- sequential circuit test pattern generation is not required

- Test pattern generation need only be done for the combinational circuits

- the bistable elements can be accessed and tested directly

- converting between parallel and serial data

- Two approaches

- shift register (scan-path method)

- multiplexer

Copyright 2019, M. Tahoori

TDS I: Lecture 12

10

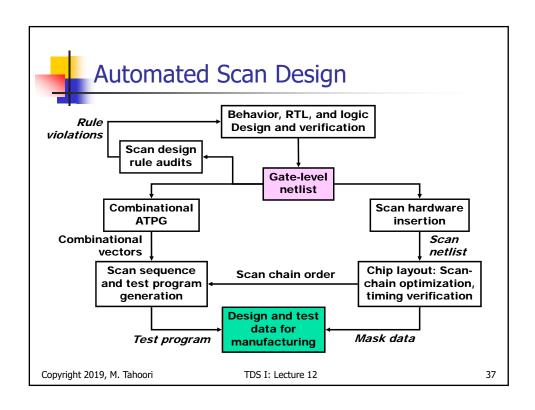

#### Scan Design

- Circuit is designed using pre-specified design rules.

- Test structure (hardware) is added to the verified design:

- Add a test control (TC) primary input.

- Replace flip-flops by *scan flip-flops* (SFF) and connect to form one or more shift registers in the test mode.

- Make input/output of each scan shift register controllable/observable from PI/PO.

- Use combinational ATPG to obtain tests for all testable faults in the combinational logic.

- Add shift register tests and convert ATPG tests into scan sequences for use in manufacturing test.

Copyright 2019, M. Tahoori

TDS I: Lecture 12

11

## Scan Design Rules

- Use only clocked D-type of flip-flops for all state variables.

- At least one PI pin must be available for test; more pins, if available, can be used.

- All clocks must be controlled from PIs.

- Clocks must not feed data inputs of flip-flops.

Copyright 2019, M. Tahoori

TDS I: Lecture 12

12

#### Scan Path Method

- Circuit with two modes of operation

- Normal functional mode

- Test mode

- Circuit bistables are interconnected into a shift register

- With the circuit in test mode

- It is possible to shift an arbitrary test pattern into the bistables

- By returning the circuit to normal mode for one clock period

- The combinational circuitry acts upon the bistable contents and primary input signals,

- Stores the results in the bistables

- Circuit is then placed into test mode

- It is possible to shift out the contents of the bistables and

- Compare these contents with the correct response

Copyright 2019, M. Tahoori

TDS I: Lecture 12

13

# Scan Path Methods for Flip-Flop Machines

Copyright 2019, M. Tahoori

TDS I: Lecture 12

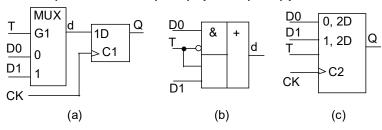

## Scan Path Methods for Flip-Flop Machines

- Each of the circuit flip-flops is replaced by

- Multiplexed data flip-flop (MD flip-flop)

- (a) flip-flop with multiplexer (MUX)

- (b) multiplexer circuit diagram

- (c) symbol for multiplexed data flip-flop (MD flip-flop)

Copyright 2019, M. Tahoori

TDS I: Lecture 12

15

## **MD Flip-flop Architectures**

- A multiplexer is placed at the data input of a flipflop

- To permit a selection of two different data inputs

- d0: (normal system operation)

- d1: (test mode).

- The choice of data input is based on the value of the control input, T.

- When T=0, data is gated from the d0 input upon an active clock transition.

- Data is taken from d1 if T is equal to 1.

Copyright 2019, M. Tahoori

TDS I: Lecture 12

16

## **MD Flip-flop Architectures**

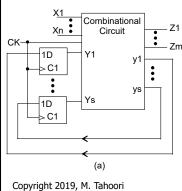

- (a) General structure of a flip-flop finite state machine

- (b) MD-flip-flop scan path architecture

TDS I: Lecture 12

## MD Full-Scan Design

- *Primary inputs* (PIs)

- the external inputs to the circuit

- can be set to any required logic values

- set directly in parallel from the external inputs

- Pseudo primary inputs (PPIs)

- the scan cell outputs

- can be set to any required logic values

- are set serially through scan chain inputs

- Primary outputs (POs)

- the external outputs of the circuit

- can be observed

- are observed directly in

- parallel from the external outputs

- Pseudo primary outputs (PPOs)

- the scan cell inputs

- can be observed

- are observed serially through scan chain outputs

Copyright 2019, M. Tahoori

TDS I: Lecture 12

18

#### MD Flip-flop Architectures

- general structure of a flip-flop finite state machine

- CK is the clock input,

- *X1*, ..., *Xn* are the primary inputs

- *Z1*, ..., *Zm* are the primary outputs.

- There are *s* D-flip-flops corresponding to internal variables *y1*, ..., *ys*.

- scan path architecture using MD flip-flops

- One additional input, the T input, has been added

- T = 0: The upper data inputs (y1, ..., ys) act as the flip-flop D inputs

- T = 1: The lower data inputs become the flip-flop D inputs.

- $D_i = Q_{i-1}$  for i from 2 to s, and a shift register is formed

- The primary input Xn is connected to D1 becoming the shift register input

- Qs, the shift register output, appears at the primary output Zm.

Copyright 2019, M. Tahoori

TDS I: Lecture 12

19

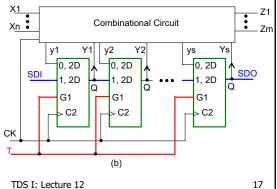

## Testing of the combinational logic

- Setting T = 1 (scan mode)

- 2. Shifting the test pattern  $y_i$  values into the flip-flops.

- 3. Setting the corresponding test values on the Xi inputs.

- Setting T=0 and, after a sufficient time for the combinational logic to settle, checking the output  $Z_k$  values.

- 5. Applying a clock signal to CK.

- Setting T = 1 and shifting out the flip-flop contents via  $Z_m$ .

- The next  $y_i$  test pattern can be shifted in at the same time.

- The  $y_j$  values shifted out are compared with the good response values for  $y_i$ .

Copyright 2019, M. Tahoori

TDS I: Lecture 12

20

#### Testing Flip-Flops in Scan Chain

- Scan register must be tested prior to application of scan test sequences

- To verify the possibility of shifting both a 1 and a 0 into each flip-flop

- Shifting a string of 1s and then a string of 0s through the shift register

- More complex pattern such as 00110011... (of length  $n_{\rm sff}$ +4) may be necessary

- To verify that all possible data transitions are possible

- These tests are often called *flush tests*

- Test sequences for scan flip-flops based on checking experiments

- Checking experiments are exhaustive tests for sequential circuits and detect all combinational faults

Copyright 2019, M. Tahoori

TDS I: Lecture 12

22

#### **Total Scan Test**

- Total scan test length:

- $(n_{\text{comb}} + 2) n_{\text{sff}} + n_{\text{comb}} + 4 clock periods$ .

- Example:

- 2,000 scan flip-flops, 500 comb. vectors,

- total scan test length  $\sim 10^6$  clocks.

- Multiple scan registers reduce test length.

Copyright 2019, M. Tahoori

TDS I: Lecture 12

23

#### **Issues**

- The MD-flip-flop based scan path architecture does not need to route any extra clock

- However, the test signal T has to be routed to all flip-flop

- Depending on the layout, the routing of the test signal T with proper skew control limits the speed at which scan shift can be done

- Scan speeds between 10 MHz to 200 MHz aren't uncommon

- Another factor that limits the speed at which the scan chains can be operated is the amount of power dissipation during scan

Copyright 2019, M. Tahoori

TDS I: Lecture 12

24

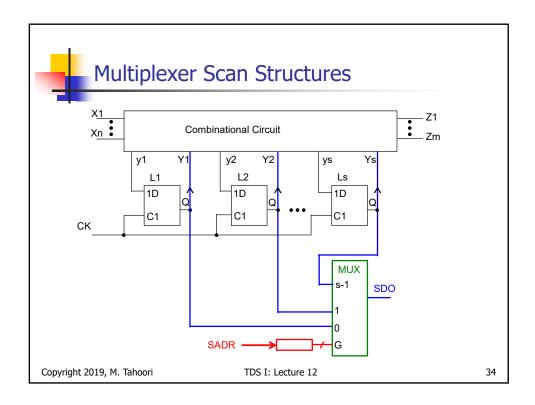

#### **Multiplexer Scan Structures**

- Parallel data can be serialized with a multiplexer rather than a shift register

- Use of more than one scan-out point increases the speed of scanning,

- But does increase the number of I/O connections required.

- One possibility for avoiding this increase is to place multiplexers on output pins to permit some of the output pins to be used both for system output and for scanning out test data

- With a multiplexer scan structure, nodes other than latch outputs can be accessed

- The scanning operation can take place while the system is operating

Copyright 2019, M. Tahoori

TDS I: Lecture 12

33

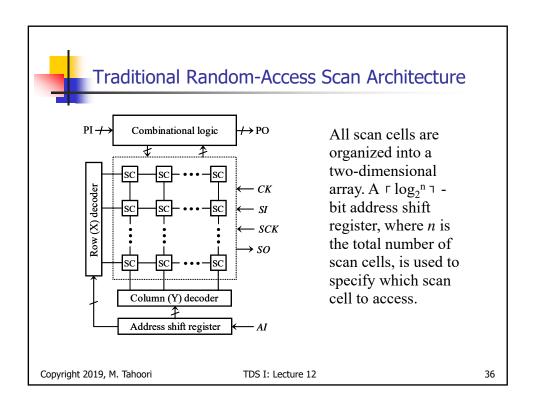

## Random Access Scan Design

- Multiplexer structure improves the observability of a design

- But does nothing for the controllability

- Setting of the system latches can be accomplished with a demultiplexer

- Random access scan design

- Multiplexer to read out bistables (observability)

- Demultiplexer to set bistables (controllability)

- Addressable latch

Copyright 2019, M. Tahoori

TDS I: Lecture 12

35

#### Scan Economics

- Additional circuitry is added to each flip-flop or latch

- One or more additional circuit pins are required

- The number of additional pins required for scan test has a direct relationship with the test time

- Testing time is increased by the need to shift the test patterns into the flip-flops serially

- The modified circuit requires shorter test sets than the original circuit

Because only combinational logic test patterns are used

- There can be a performance penalty.

- The speed of normal operation may be decreased due to increased propagation delay in the scan path latches or flip-flops

- Available functional area can be reduced due to the increased interconnect

- Timing closure can be a problem

- Power dissipation during scan

Copyright 2019, M. Tahoori

TDS I: Lecture 12

38

#### Summary

- Scan is the most popular DFT technique:

- Rule-based design

- Automated DFT hardware insertion

- Combinational ATPG

- Advantages:

- Design automation

- High fault coverage; helpful in diagnosis

- Hierarchical scan-testable modules are easily combined into large scan-testable systems

- Moderate area (~10%) and speed (~5%) overheads

- Disadvantages:

- Large test data volume and long test time

- Basically a slow speed (DC) test

Copyright 2019, M. Tahoori

TDS I: Lecture 12

39