| Summar                                                     | y: Ad-    | Hoc DFT Techniques                                                                                                     |   |

|------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------|---|

| Feature                                                    |           | Ad hoc Technique                                                                                                       |   |

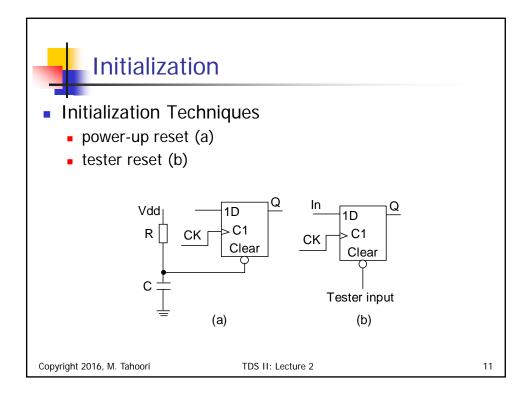

| Unknown initial                                            | state     | Initialization circuitry                                                                                               |   |

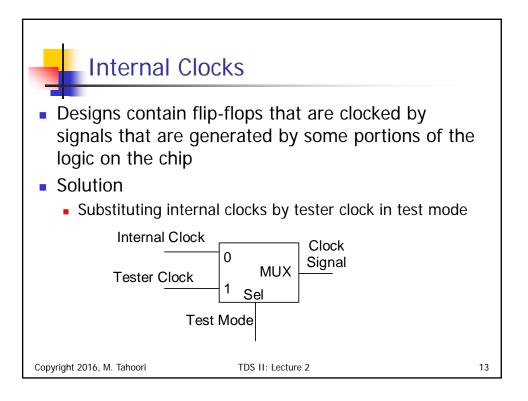

| Internal cloc                                              | k         | Circuitry to disconnect internal clock and substitute tester clock                                                     |   |

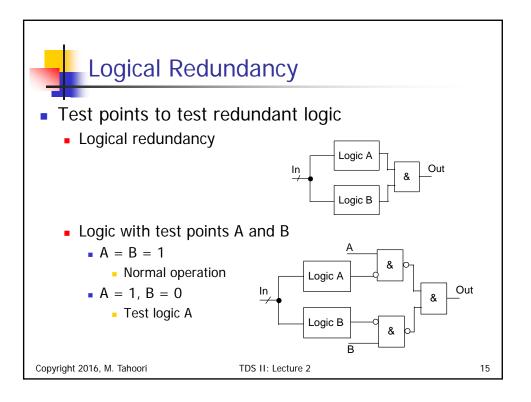

| Logical redunda                                            | ancy      | Avoid or add test points                                                                                               |   |

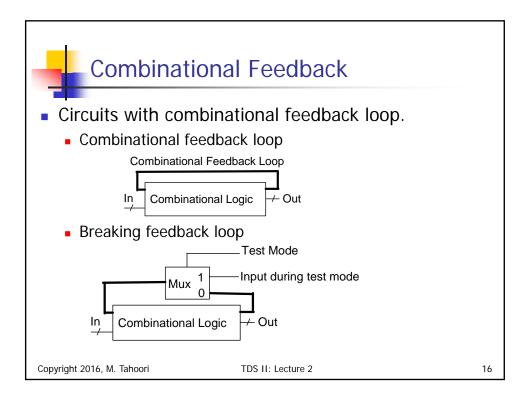

| Feedback loo                                               | ps        | Circuitry to permit tester to break feedback loop                                                                      |   |

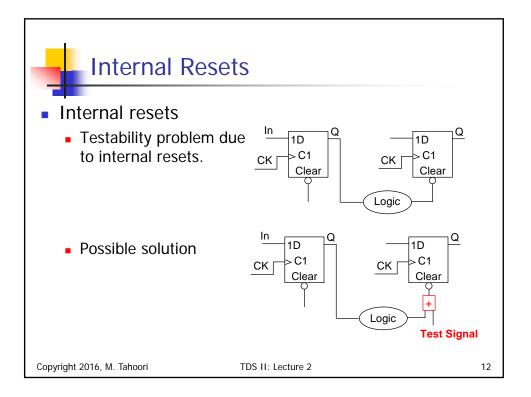

| Internally generated<br>asynchronous set<br>inputs of flip | and Reset | Circuitry to permit tester not to allow the tester not<br>to allow these signals to set/reset flip-flops durin<br>test |   |

| Wired logic                                                |           | Avoid                                                                                                                  |   |

| Bidirectional I/C                                          | pins      | Circuitry to permit tester to configure them to operate in one direction                                               |   |

| Tristate drivers ar<br>transisto                           |           | Circuitry to permit tester to configure them so that<br>only 1 driver drives the bus                                   |   |

| Copyright 2016, M. Tahoori                                 |           | TDS II: Lecture 2                                                                                                      | 1 |