# Logic BIST Architectures

#### Four Types of BIST Architectures:

- No special structure to the CUT

- Make use of scan chains in the CUT

- Configure the scan chains for test pattern generation and output response analysis

- Use concurrent checking circuitry of the design

Copyright 2016, M. Tahoori

TDS II: Lecture 7

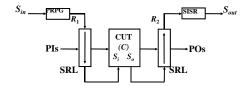

# Centralized and Separate Board-Level BIST (CSBL)

- Two LFSRs and two multiplexers are added to the circuit.

- The first LFSR acts as a PRPG, the second serves as a SISR.

- The first multiplexer selects the inputs, another routes the PO to the SISR.

**CSBL** Architecture

[Benowitz 1975]

Copyright 2016, M. Tahoori

TDS II: Lecture 7

\_

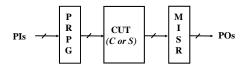

## Built-In Evaluation and Self-Test (BEST)

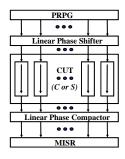

- Use a PRPG and a MISR.

- Pseudo-random patterns are applied in parallel from the PRPG to the chip primary inputs (PIs)

- MISR is used to compact the chip output responses

**BEST Architecture**

[Perkins 1980]

Copyright 2016, M. Tahoori

TDS II: Lecture 7

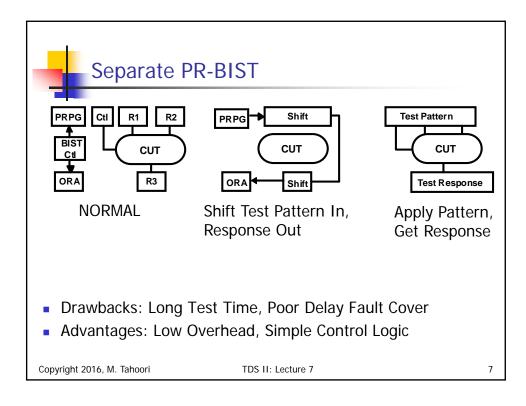

#### Separate PR-BIST

- In addition to the internal scan chain, an external scan chain comprising all primary inputs and primary outputs is required.

- The External scan-chain input is connected to the scan-out point of the internal scan chain.

**LOCST Architecture**

[Eichelberger 1983]

Copyright 2016, M. Tahoori

TDS II: Lecture 7

6

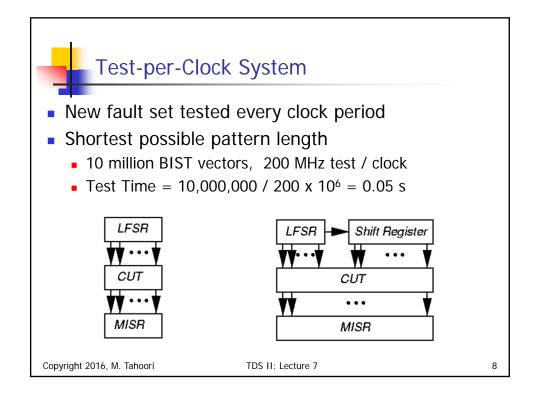

## Test-per-Scan System

- New fault tested during 1 clock vector with a complete scan chain shift

- More time required per test than test-per-clock

- Advantage:

- Combination of scan chains and MISR reduces MISR bit width

- Disadvantage:

- Much longer test pattern set length, causes fault simulation problems

- Input patterns time shifted & repeated

- Become correlated reduces fault detection effectiveness

- Use XOR network to phase shift & decorrelate

Copyright 2016, M. Tahoori

TDS II: Lecture 7

q

#### **STUMPS**

- Self-Test Using MISR and Parallel Shift register sequence generator

- Originally proposed to reduce overhead of LFSR/MISR for application to testing multi-chip boards, each of which has only the Shift Registers

- Can also be used on a single chip with multiple scan chains

Copyright 2016, M. Tahoori

TDS II: Lecture 7

10

Lecture 7 5

## STUMPS Example

- SR1 ... SRn 25 full-scan chains, each 200 bits

- 5000 chip outputs, need 25 bit MISR (not 5000 bits)

**STUMPS**

A STUMPS-based Architecture

Copyright 2016, M. Tahoori

TDS II: Lecture 7

11

#### **STUMPS**

- Test procedure:

- Scan in patterns from LFSR into all scan chains (200 clocks)

- Switch to normal functional mode and clock 1 x with system clock

- Scan out chains into MISR (200 clocks) where test results are compacted

- Overlap Steps 1 & 3

- Requirements:

- Every system input is driven by a scan chain

- Every system output is caught in a scan chain or drives another chip being sampled

Copyright 2016, M. Tahoori

TDS II: Lecture 7

12

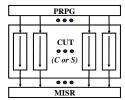

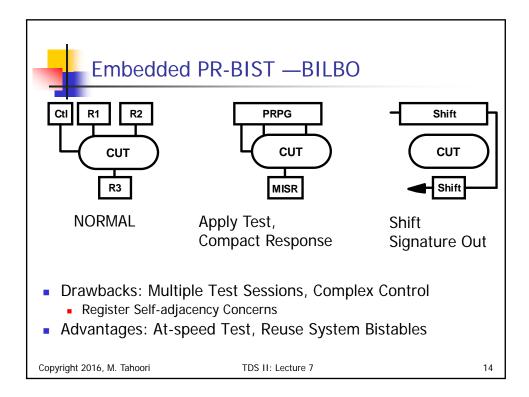

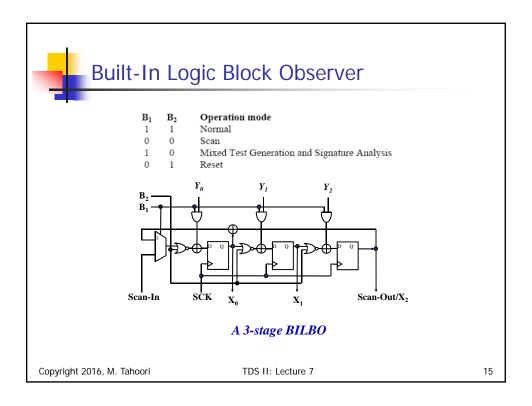

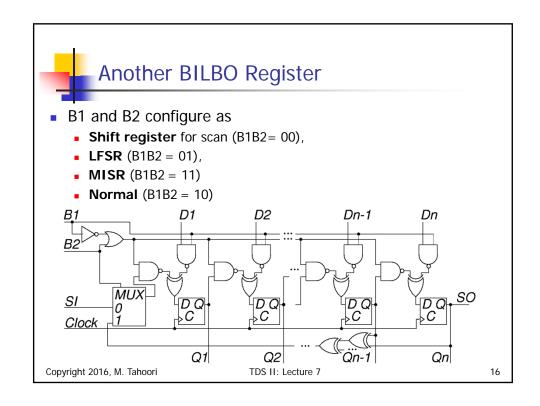

## Built-In Logic Block Observer (BILBO)

- The architecture applies to circuits that can be partitioned into independent modules (logic blocks).

- Each module is assumed to have its own input and output registers (storage elements)

- Or such registers are added to the circuit where necessary.

- The registers are redesigned so that for test purposes they act as PRPGs or MISRs.

Copyright 2016, M. Tahoori

TDS II: Lecture 7

13

Lecture 7 8

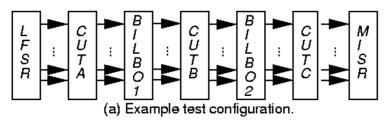

# Example BILBO Usage

- SI Scan In

- SO Scan Out

- Characteristic polynomial: 1 + x + ... + x<sup>n</sup>

- CUTs A and C: BILBO1 is MISR, BILBO2 is LFSR

- CUT B:

BILBO1 is LFSR, BILBO2 is MISR

Copyright 2016, M. Tahoori

TDS II: Lecture 7

17

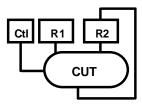

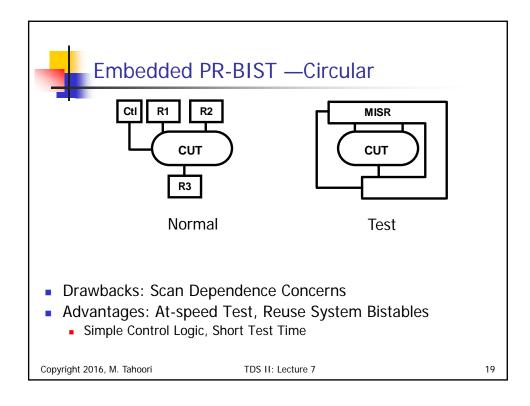

# Register self-Adjacency

- Register R2 is self-adjacent

- It should act as LFSR and MISR at the same time

- Cannot use BILBO register

Copyright 2016, M. Tahoori

TDS II: Lecture 7

18

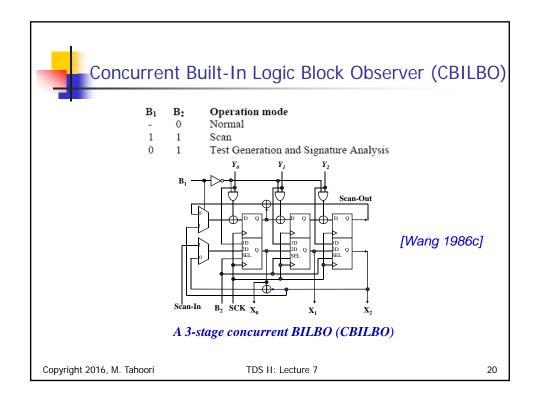

# Summary

| Architecture | Level  | TPG      | ORA     | Circuit | BIST           |

|--------------|--------|----------|---------|---------|----------------|

| CSBL         | B or C | PRPG     | SISR    | C or S  | Test-Per-Clock |

| BEST         | B or C | PRPG     | MISR    | C or S  | Test-Per-Clock |

| LOCST        | С      | PRPG     | SISR    | С       | Test-Per-Scan  |

| STUMPS       | B or C | PRPG     | MISR    | С       | Test-Per-Scan  |

| BILBO        | С      | PRPG     | MISR    | С       | Test-Per-Clock |

| CBILBO       | C      | EPG/PEPG | MISR    | С       | Test-Per-Clock |

| CSTP         | С      | PRPG     | MISR    | C or S  | Test-Per-Clock |

| CSV          | С      | PRPG     | Checker | C or S  | Test-Per-Clock |

B: board-level testing C: combinational circuit S: sequential circuit

#### Representative Logic BIST Architectures

Copyright 2016, M. Tahoori

TDS II: Lecture 7

23